半導體先進封裝生態系 英特爾帶動產業制定標準開發迎合未來運算所需

▲英特爾公司資深副總裁暨封裝∕測試開發事業部總經理Babak Sabi以工程專家與產業領導者的身分,於四月份舉辦的2022國際超大型積體電路技術研討會中說明先進封裝生態系所遇到的挑戰,並以英特爾的解決方案為例。(圖/英特爾提供)

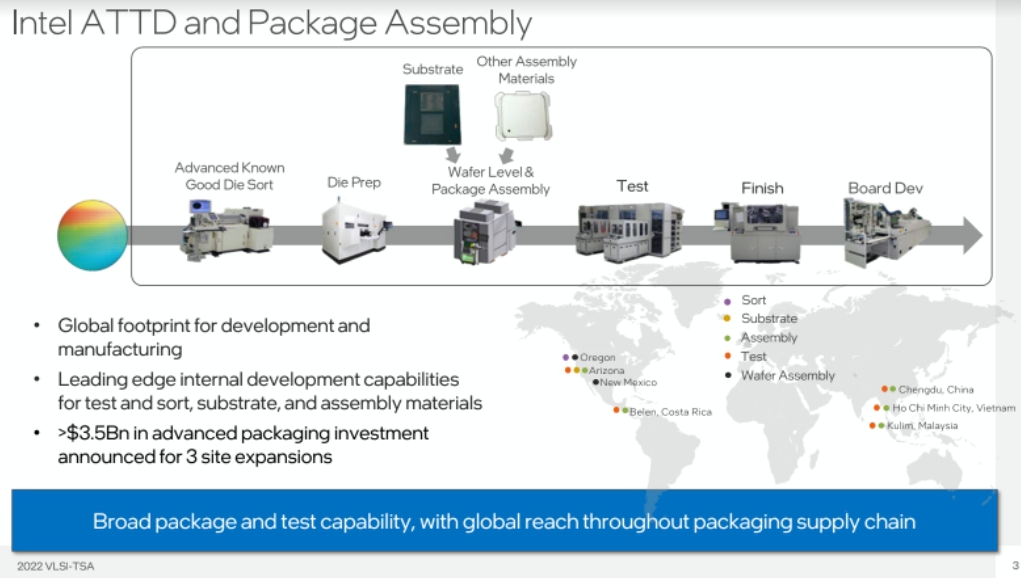

【焦點時報/記者羅蔚舟報導】四月份舉辦的2022國際超大型積體電路技術研討會,英特爾公司資深副總裁暨封裝∕測試開發事業部總經理Babak Sabi,以工程專家與產業領導者的身分,說明先進封裝生態系所遇到的挑戰,並以英特爾的解決方案為例,闡述現在以及未來的推動方向,更要帶動整個產業的標準化,滿足未來運算需求。

▲英特爾公司資深副總裁暨封裝∕測試開發事業部總經理Babak Sabi以工程專家與產業領導者的身分,於四月份舉辦的2022國際超大型積體電路技術研討會中說明先進封裝生態系所遇到的挑戰,並以英特爾的解決方案為例。(圖/英特爾提供)

Babak Sabi表示,隨著數位時代對於運算需求的增長,處理器核心越來越多、效能越來越強大,一個關鍵問題將逐漸浮上檯面:「該如何提供足夠的資料吞吐量,才能夠維持高效能、高輸出的運算結果?」大數據進一步催生高頻寬、大容量記憶體的需求,但現實情況無法隨心所欲地提升傳輸所需的功耗,需以有效率的方式傳輸大量資料。

位於處理器核心內部的快取記憶體為靜態記憶體(SRAM)結構,儲存單一位元通常需要6個電晶體,享有幾乎與核心一樣快的速度,倘若加大快取記憶體,則十分耗能且需要不小的矽晶片面積;在處理器封裝之外的系統記憶體為動態記憶體(DRAM)結構,儲存單一位元僅需要1個電晶體和1個電容,設計上針對容量最佳化,提升速度反而不是件容易的事。在這兩者之間,HBM(High Bandwidth Memory)以TSV(Through-Silicon Via)堆疊多個晶粒,單一封裝使用1024bit匯流排寬度,以此提供更大的空間和更高的頻寬,但需要更高密度、更先進的封裝技術,盡可能地將HBM封裝至靠近處理器之處。

Babak Sabi指出,追求降低每單位位元移動的功耗需求,並持續推動互連頻寬與密度,不僅要求先進封裝需達成全面性的創新,更需要整個產業生態系一同合作,從系統、電路板、封裝再到複合晶粒體(die complex),都有要跨越的城池。英特爾已有推動系統、電路板、封裝、晶粒開發和整合的路線圖,與先進封裝有關的內容包含:系統層級—透過改良後的晶粒和封裝架構,降低每單位位元移動時所需功耗;電路板層級—整合光學傳輸,以便繼續提升頻寬速度與密度;封裝層級—使用次世代熱界面材料(TIM)改善散熱、透過Coax MIL提升電源傳輸效率、共同封裝光學傳輸元件;複合晶粒體—提升晶粒間的互連頻寬,並制定相互溝通的產業標準(如UCIe)。

Babak Sabi表示,晶片分拆理念不僅能夠針對某個功能區塊使用最佳製程生產,更能夠將來自多家廠商的晶片整合至單一封裝之中,大幅度提升良率和上市時間。為了落實真正的晶粒「隨插即用(Plug & Play)」,制定統一的晶粒間傳輸規範是首要之務。英特爾所主導的UCIe(Universal Chiplet Interconnect Express)獲得包含AMD、Arm、ASE、Google Cloud、Meta、Microsoft、Qualcomm、Samsung、TSMC等眾多廠商的支持,讓來自不同廠商、代工廠的晶粒能夠在封裝內相互溝通。

Babak Sabi說,UCIe汲取十分成熟的PCI Express和Compute Express Link產業標準優勢,為生態系注入標準化、開放式、多種協定之外,尚有許多特色,例如提升傳輸效率和2ns以下的延遲時間、高密度並列式傳輸、NRZ編碼支援至32GT/s,並支援多樣化的裝置、不同的製程,以及各式各樣的先進封裝。在標準封裝當中,可達成100μm~130μm凸塊間距、10mm~25mm通道長度,每mm最高可提供224GB/s速率;轉進先進封裝(例如EMIB),凸塊間距則能夠縮減至25μm~55μm,每mm速率則大幅度提升至1317GB/s,有助於實現高密度、高效能的先進封裝產品。

Babak Sabi強調,UCIe更是個持續演進,滿足未來10年預期需求的開放式標準,透過不斷提升每單位晶片面積的頻寬,與產業界的實際應用相互契合。先進封裝的未來需要產業夥伴的共同參與,真正完成「隨插即用的標準化」。